| Name | Key |  |

|------|-----|--|

|      |     |  |

EE3610 Midterm Exam (Fall 2012). 6 Pages. Open book. Open Notes. Closed Internet. Cheating will not be tolerated and will result in grade of 0 for this exam.

| Part | 1 | Short | Ans | wer |

|------|---|-------|-----|-----|

|      |   |       |     |     |

| aı  | t 1. Short Miswer.                                                                                                                                                          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l.  | (2 pts) There are two predominant hardware description languages. Name them.                                                                                                |

|     | (1) UHDC<br>(2) Verilog                                                                                                                                                     |

| )   | (3 pts) What is the difference between a structural and a behavioral model?                                                                                                 |

|     | Behavioral describes what the model does, Structural                                                                                                                        |

|     | describes how (components & interconnect).                                                                                                                                  |

|     |                                                                                                                                                                             |

| 3.  | <ul><li>(2 pts) If the order of two concurrent statements in a VHDL model are changed:</li><li>(a) The behavior of the model is certain to change.</li></ul>                |

|     | (b) The behavior of the model may change.                                                                                                                                   |

|     | The behavior of the model is certain not to change.                                                                                                                         |

|     | (d) A paradox is generated that may destroy the fabric of the universe.                                                                                                     |

| 4.  | (2 pts) (true false) A process that is supposed to model combinational logic should drive all the outputs each time it runs, no matter what the inputs are.                 |

| 5.  | (2 pts) (true false) A process that is supposed to model sequential logic should drive all the outputs each time it runs, no matter what the inputs are.                    |

| 5.  | (2 pts) (true/false) Pipelining is a technique that decreases latency (the time it takes to get a result) but also decreases throughput (the number of results per second). |

| 7.  | (2 pts) (true/false) The first programmable electronic logic device was the ROM.                                                                                            |

| 8.  | (2 pts) (true/false) The principal difference between a PLA and a PAL is the PLA has a programmable OR array, but in the PAL the OR array is fixed.                         |

| 9.  | 1 / 11                                                                                                                                                                      |

|     | and 2 outputs.  (a) How many output pins must be dedicated to state bits plus outputs?                                                                                      |

|     | (a) How many output pins must be dedicated to state bits plus outputs?                                                                                                      |

|     | (c) How many unused pins will there be?/_                                                                                                                                   |

| 10. | (2 pts) (true/false) an FPGA consists predominantly of programmable logic blocks and programmable interconnections.                                                         |

| 11. | (2 pts) What does BCD stand for?                                                                                                                                            |

|     | Binary Coded Decimal                                                                                                                                                        |

| 12. | (2 pts) Under the IEEE 1164 standard, what is the state of a signal that is simultaneously driven with a '0' and an 'Z'?                                                    |

| 13. | (2 pts) (true/false) In VHDL, it is impossible to have a constant, signal or variable that is an array without declaring the array type first.                              |

14. (3 pts) (true/false) I would like another 3 points on this exam.

## Part 2 - Problems

15. (5 pts) Loop and give the simplest SOP expression for the given Variable Entered map

| AB |    |    |    |    |

|----|----|----|----|----|

| CD | 00 | 01 | 11 | 10 |

| 00 | Ē  | Ē  | 0  | 0  |

| 01 | X  | 1) | Е  | E  |

| 11 | 1  | 0  | X  | 0  |

| 10 | 0  | 0  | 0  | X  |

|    |    |    |    |    |

16. (5 pts) Write a VHDL <u>process</u> (not the whole module) to model a T flip-flop with an asynchronous reset.

## end process;

17. (5 pts) Write a <u>concurrent statement</u> to model a 4-bit adder with carry input. Assume that addends (A and B) are unsigned(3 downto 0) and the carry in (Ci) is std\_logic. The output is a 5-bit sum (S), whose type is unsigned(4 downto 0).

18. (15 pts) Each of the VHDL code fragments below can be used to model a physical device. Tell what kind of device it is (e.g. D- flip-flop, MUX, gate, shift register, etc.) and name its features, if any (e.g. synchronous reset, asynchronous reset, clock enable, parallel load, number of MUX inputs, etc.)

```

(a) process(A, E)

begin

if E = '1' then

Y \leq A:

else

Y \leq 'Z';

end if:

end process;

Device Tri-state buffer

(b)process(CLK)

begin

if rising edge(CLK) then

if rst = '1' then

Q \le (others = >'0');

elsif PE = '1' then

Q <= ParallelData;

elsif SH= '1' then

Q \leq DSR \& Q(7 \text{ downto } 1);

end if;

end if;

end process;

Device Parallel - in Shift register with Synchronous Reset

(c) Y \le 10 when S = "00" else

I1 when S= "01" else

I2 when S="10" else

Device 4-1 Mux

```

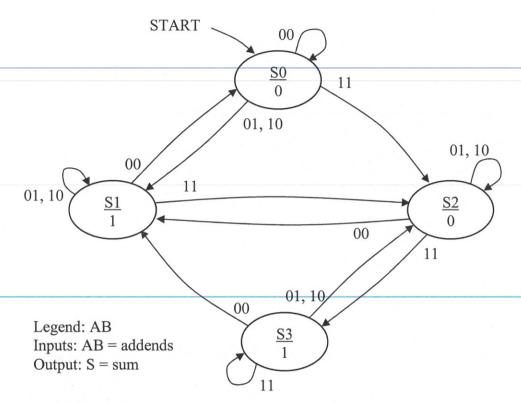

19. The state diagram below represents a serial adder. (Addends A and B arrive one bit at a time, least significant bit first, and the sum, S, is delivered in the same manner.)

(a). (4 pts) Write the entity declaration for this module. Give the module the name ser\_add.

(b). (4 pts) Declare any signals, types, constants, etc. you will need for this module between the <u>architecture</u> and <u>begin</u> keywords below:

architecture behavioral of ser\_add is

(c). (4 pts) Write VHDL code to model the state register.

(d). (8 pts) Write VHDL code to model the next state decoder. To save time, you may replace states S1 and S2 in the case statement with when S1=>... and when S2=>... respectively.

(e). (4 pts) Write a VHDL statement to model the output decoder

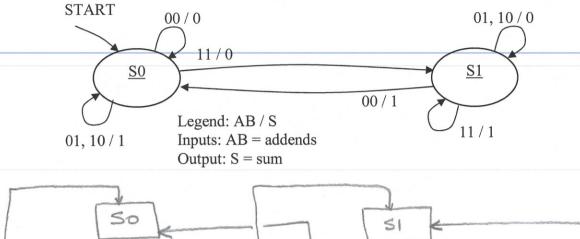

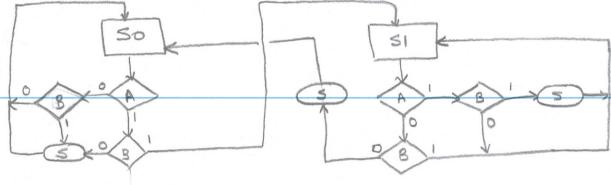

20. (10 pts) A Mealy version of the serial adder is given below. Draw an SM chart that is equivalent to this state diagram.

- 21. (2 pts) Comparing the Moore state machine in problem 19 with the Mealy state machine in problem 20:

- (a) The Moore state machine generates its output earlier than the Mealy state machine.

- (b) The Mealy state machine generates its output earlier than the Moore state machine.

- (c) Both state machines generate their output at the same time.

Extra Credit (5 pts) Draw a state diagram similar to the one in problem 20 that implements a serial subtractor.